삼성전자, 12단 적층 HBM3E 개발 성공…업계 최대 36GB 용량 구현

6세대 HBM도 개발 中…HBM 공급 역량도 업계 최고 수준으로

HBM 공정 핵심 기술인 적층 기술로 반도체 시장 꾸준히 어필

서울 서초동 삼성서초사옥 앞에서 삼성 깃발이 휘날리고 있다.ⓒ데일리안 홍금표 기자

서울 서초동 삼성서초사옥 앞에서 삼성 깃발이 휘날리고 있다.ⓒ데일리안 홍금표 기자

삼성전자가 업계 최초로 36GB(기가바이트) 12단 적층 HBM3E 개발에 성공하며 차세대 HBM(고대역폭메모리) 시장 지각 변동을 예고했다. 삼성전자가 한 발 앞서 AI용 반도체 장악력을 확대한 SK하이닉스를 제치고 반격에 성공할 수 있을지 관심이 쏠린다.

삼성전자는 24Gb(기가비트) D램 칩을 TSV(실리콘 관통 전극) 기술로 12단까지 적층해 업계 최대 용량인 36GB HBM3E 12H를 구현했다고 27일 밝혔다.

HBM3E 12H는 초당 최대 1280GB의 대역폭과 현존 최대 용량인 36GB을 제공해 성능과 용량 모두 전작인 HBM3(4세대 HBM) 8H(8단 적층) 대비 50% 이상 개선된 제품이다.

AI반도체 시장이 2030년까지 10배 이상 커질 것으로 예상되면서 AI 서비스를 제공하는 고객들의 고용량 솔루션의 니즈가 커지는 가운데, 삼성전자의 HBM3E 12단은 그런 요구에 부합할 수 있는 제품으로 주목을 받는다.

실제 삼성전자의 HBM 비트 판매량은 매 분기 기록을 경신 중이다. 2023년 4분기에는 전분기 대비 40% 이상 성장했으며, 전년 동기 보다 약 3.5배 규모로 성장했다.

차세대 HBM 시장 우위? 삼성 "6세대까지 개발중"

삼성전자는 HBM3(4세대 HBM)에서의 12H(12단 적층) 양산 경험을 통해 얻은 노하우와 적층 기술력 등을 통해, 차세대 HBM 경쟁에서 우위를 차지할 것으로 기대한다. 양적으로나 기술적으로나 경쟁사를 압도할 수 있다는 자신감이다.

올해 삼성은 HBM 공급 역량을 업계 최고 수준으로 유지하기 위해 작년 대비 2.5배 이상 생산능력(캐파)을 확보해 운영할 계획이다. 칩 적층에 있어 요구되는 TSV 공정에 대한 캐파 역시 업계 우위를 유지하고 있다는 설명이다. 이를 바탕으로 HBM3E 사업화 및 하반기 3E 12단 적층 전환 가속화를 추진, HBM 경쟁력을 적극 강화한다는 방침이다.

삼성전자는 HBM3E 샘플 공급과 상반기 양산에 이어 HBM3E의 안정적인 양산 체계를 갖춰 나갈 예정이다. 다음 세대인 HBM4(6세대 HBM)도 2025년 샘플링과 2026년 양산 목표로 개발을 진행중이다.

특히 HBM4부터는 고객 맞춤형에 대한 HBM 요구에 대한 대응이 증가하며 이를 위해 삼성전자는 표준 제품뿐만 아니라 선단 로직칩을 추가해 고객별로 최적화된 '커스텀 HBM' 제품으로 주요 고객사들의 니즈를 충족시킬 계획이다.

시장조사기관 트랜드포스는 HBM4에서는 12단, 16단 적층으로 확장될것으로 전망했다. 이 과정에서 하이브리드 본딩 기술이 요구될 것으로 봤다.

미래 HBM 제품의 두께 제약 극복이 필요한 HBM4 16단 초고용량 제품에서도 삼성전자는 칩과 칩 사이 갭을 완전히 없애고, 칩을 완전히 붙이는 신공정을 개발중이다. 미래 시장의 수요에 대응하기 위한 기반 기술에 대비해 HBM 선도업체로서의 리더십을 강화해 나간다는 계획이다.

AI 시장 고도화로 고용량 HBM 수요 증가…삼성전자, 적층기술로 선도

삼성전자는 메모리 업계 리더로서 우수한 기술력을 바탕으로 계속해서 발전해가는 AI시장에서 요구하는 고용량에 대한 니즈에 부합하기 위해 노력하고 있다. 첫 걸음으로 12단 고단 HBM 제품을 상용화를 선도할 예정이다.

HBM4에서는 ▲고용량화 ▲고객 개별 맞춤형이 요구되면서 삼성전자는 준비된 기술력을 바탕으로 맞춤형 솔루션을 제공할 계획이다. HBM 양산 공정에서 핵심이 되는 D램 적층 기술은 삼성전자가 다년간 양산하며, 수율과 성능을 확인했다.

HBM은 수직적으로 D램 칩을 적층하고 TSV를 통해 연결한다. 상하부 칩의 TSV를 연결하기 위해 '마이크로 범프'를 사용하게 되는데 이때 중요한 것이 '마이크로 범프' 간에 갭을 채우는 기술이다.

삼성전자가 독자적으로 개발한 NCF기술은 필름을 사용해 갭을 채우기 때문에 근본적으로 갭 내 공극(void)가 없고 열과 압력을 사용해 칩을 연결하는 '써머컴프레션' 공정 또한 이미 다년간 양산을 통해 수율과 성능에 문제가 없음을 확인했다.

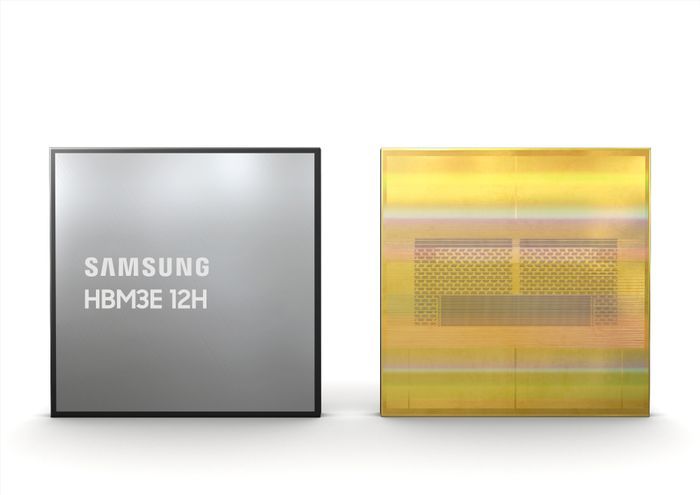

HBM3E 12H D램 제품 이미지ⓒ삼성전자

HBM3E 12H D램 제품 이미지ⓒ삼성전자

NCF 공정은 접합 물질인 솔더 표면의 산화막 제거 기능이 포함돼 있어, 본딩 시 발생 되는 솔더 산화막 제거를 위해 사용되는 세정, 가열 등의 부가 공정이 필요 없다.

또 칩을 고속으로 정밀하게 적층하는 공정과 솔더를 접합하는 공정을 구분해 최적의 공정과 설비를 개발해 충분한 경쟁력을 갖춘 생산성을 확보했다. 삼성전자의 NCF 기술력은 12단 제품에서 그 경쟁력이 더욱더 강화될 것으로 기대를 모은다.

올해부터 채용이 증가할 것으로 전망되는 12단 HBM 제품의 경우, 스택 수 증가에 따른 칩 두께 감소로 칩 휘어짐에 기인한 기술적 문제들이 발생할 수 있다.

삼성전자 NCF 기술은 칩 전면을 열과 하중을 인가해 본딩하는 방식이기 때문에, 칩의 휘어짐을 상대적으로 용이하게 제어할 수 있어, 12단 제품에서의 삼성전자 NCF 기술의 경쟁력이 부각될 것이라는 전망이다.

이 뿐 아니라 삼성은 미래 HBM 제품의 두께 제약 극복이 필요한 HBM4 16단 제품에서도 칩간 갭을 완전히 없애고 칩과 칩을 완전히 붙이는 신공정을 개발중이다.삼성전자는 이와 같이 지속적인 신기술 확보를 통해 HBM 선도업체로서의 리더십을 강화해 나갈 방침이다.

0

0

기사 공유

댓글

-

최신순

-

찬성순

-

반대순

실시간 랭킹뉴스

실시간 랭킹뉴스

댓글 쓰기